精密电子系统中的元器件协同设计策略

在现代电子系统设计中,单一元器件难以满足全部性能需求。合理搭配薄膜精密电阻器(AR..A系列)与线艺(LINEART)滤波器,是实现高可靠性、高性能系统的关键路径。以下从设计流程、电气匹配与实测验证三方面展开论述。

1. 设计前期:明确系统需求与负载特性

- 确定信号链路中的关键节点:如前级放大、采样保持、模数转换等环节。

- 评估环境因素:是否处于高温、高湿或强电磁干扰环境?

- 识别噪声源类型:是电源噪声、开关瞬态还是射频干扰?

2. 元器件匹配原则

(1)薄膜电阻与滤波器的电气兼容性

在信号调理链中,建议遵循以下匹配规则:

- 阻抗匹配:AR..A系列电阻的标称阻值应与滤波器输入/输出端口的参考阻抗一致(如50Ω),避免信号反射。

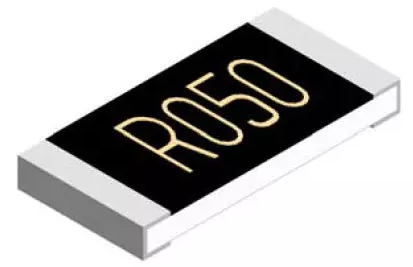

- 寄生参数控制:选择具有低寄生电感和电容的SMD封装,减少高频段性能下降。

- 共地设计:确保滤波器与电阻共享同一接地平面,防止形成地环路噪声。

(2)热管理与布局优化

由于薄膜电阻在大电流下可能发热,建议:

- 在靠近电阻位置设置散热过孔或铺铜区域。

- 将滤波器远离热源布置,避免温度影响其滤波特性。

- 采用“先滤波、再采样”的信号流向布局,提升整体信噪比。

3. 实测验证与调试方法

推荐采用如下测试流程:

- 使用网络分析仪检测滤波器的频率响应曲线,确认通带平坦度与阻带衰减。

- 通过精密数字万用表测量电阻实际阻值,验证是否在±0.1%容差范围内。

- 在真实工作温度下进行长时间运行测试(如85℃/1000小时),记录漂移数据。

- 利用示波器观察滤波前后信号波形变化,评估噪声抑制效果。

4. 成功案例分享

某医疗心电监测设备项目中,工程师将 AR..A系列 10kΩ ±0.1% 薄膜电阻与 LINEART 100MHz SMD滤波器 配合使用,成功将基线漂移降低70%,并消除因外部射频干扰导致的误报警现象,产品一次性通过FDA认证。

5. 总结:协同设计的核心理念

薄膜精密电阻与线艺滤波器并非孤立存在,而是构成信号链路的重要组成部分。只有在设计初期就统筹考虑其电气特性、热特性和布局策略,才能真正发挥“1+1>2”的协同效应,打造高稳定、高可靠的精密电子系统。